# CHAPTER 1 (6 Marks) INTRODUCTION

# **1.1 Computer Organization and Architecture**

| Computer Organization                                                                     | Computer Architecture                                                                                     |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Describes how hardware components of a computer system work together.                     | Deals with the design and specification of computer systems and components                                |

| How the computer works from an engineering perspective                                    | How to design and optimize computer systems to achieve specific goals                                     |

| How the computer do it                                                                    | What the computer does                                                                                    |

| Deals with low level design issues<br>( Logic and Circuits)                               | Deals with high level design issues<br>( system and computer)                                             |

| Structural Relationship                                                                   | Functional Behaviour                                                                                      |

| It comprises of physical units like<br>Circuit Design, Peripherals<br>ALU, CPU and Memory | It comprises logical functions such as<br>Instruction sets, Addressing Modes,<br>Data Types and registers |

| For designing a computer organization is decided after it's architecture                  | For designing a computer it's architecture is fixed first                                                 |

#### 1.2 Structure and Function

- > Structure is the way in which components relate to each other

- > Function is the operation of individual components as part of the structure

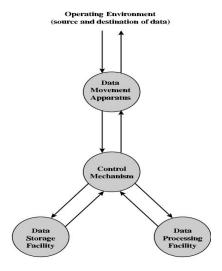

# Q. functional view and four types of operations performed in computer

### All computer functions are-:

- ➤ **Data processing:** This refers to the ability of a computer to perform calculations, manipulate information, and execute instructions based on input data.

- ▶ Data storage: Computers have various types of memory that allow them to store data either temporarily (in RAM) or permanently (on a hard drive or other storage device). This data can be accessed and manipulated as needed by the computer's processor.

- ➤ Data movement: This involves the ability of a computer to transfer data between itself and other devices or networks. This can include sending and receiving data over a network, copying files between storage devices, or even communicating with other types of hardware devices such as printers or scanners.

- ➤ Control: In order to perform these functions effectively, a computer needs to be able to manage and control its own operations. This can involve coordinating data processing tasks, managing storage resources, and controlling the flow of data into and out of the system. Control also involves managing the

interaction between the user and the computer, such as through a user interface or command line.

The four main structural components of a computer system are:

- ➤ Central Processing Unit (CPU): The CPU is the "brain" of the computer and is responsible for executing instructions and performing calculations. It contains one or more processing cores, which can execute multiple instructions simultaneously through pipelining and other techniques.

- ➤ Main Memory: Main memory, also known as random-access memory (RAM), is used to temporarily store data and instructions that the CPU is actively using. It is volatile, meaning that its contents are lost when the power is turned off.

- ➤ Input/Output (I/O): Input/output refers to the methods by which a computer interacts with the external world. Input devices such as keyboards, mice, and touchscreens allow users to enter data into the computer, while output devices such as monitors, printers, and speakers display or communicate the results of computations.

- > **System Interconnections:** System interconnections refer to the ways in which the various components of the system are connected and communicate with each other. This includes buses, switches, and other interconnect technologies that allow data to be transferred between components.

# Q. What is performance balance? why required?

Performance balance, also known as workload balancing, is the process of distributing computing tasks and resources in a system to achieve optimal performance. It involves managing the allocation of processing power, memory, storage, and network

bandwidth to ensure that all parts of the system are functioning efficiently and effectively.

Performance balance is required because modern computer systems are complex and consist of multiple interconnected components. These components, such as processors, memory, and storage devices, have different capabilities and limitations. In addition, different software applications have different demands on system resources. If these resources are not properly balanced, certain components of the system may become overloaded, leading to performance degradation and system failures.

### Q. Explain design goals and performance metrics?

Design goals are the primary objectives that a computer system architect or designer aims to achieve when creating a system. Performance metrics are measurements used to evaluate the effectiveness and efficiency of the system in meeting those design goals.

Some common design goals for computer systems include:

- ➤ **Performance:** This refers to how fast the system can perform tasks and how much work it can handle in a given amount of time.

- Reliability: This refers to the system's ability to perform consistently and predictably over time, without experiencing crashes or other errors.

- ➤ **Availability:** This refers to the system's ability to remain operational and accessible to users over time, even in the face of hardware or software failures.

- > **Security:** This refers to the system's ability to protect against unauthorized access or use, as well as its ability to maintain data privacy and integrity.

Some common performance metrics used to evaluate computer systems include:

- > **Throughput:** This refers to the amount of work that a system can perform in a given amount of time.

- Latency: This refers to the amount of time it takes for a system to respond to a request or perform a task.

- > Response time: This refers to the amount of time it takes for a user to receive a response to a request.

- > **Scalability:** This refers to the system's ability to handle increasing workloads without suffering a significant decrease in performance.

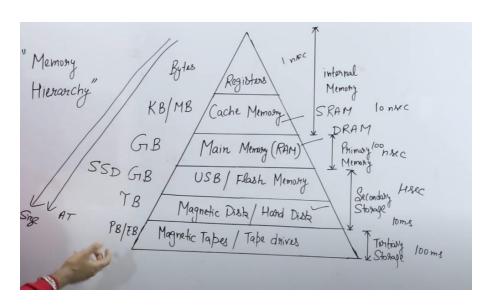

# Q. how can we maintain performance balance between processor and memory

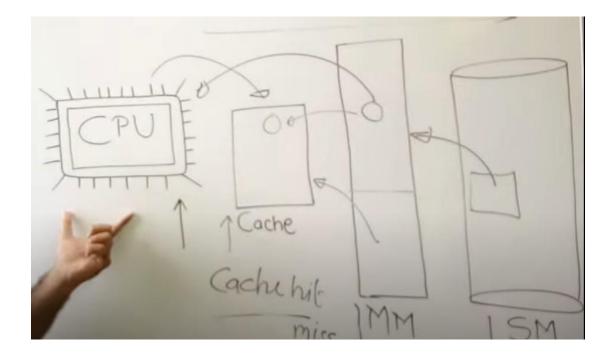

Maintaining performance balance between processor and memory is crucial for achieving optimal system performance. The processor and memory are two of the most critical components in a computer system, and their performance is closely linked. If the processor is too fast for the memory, the processor will be forced to wait for data to be fetched from memory, resulting in performance degradation. Similarly, if the memory is too slow for the processor, the processor will spend too much time waiting for data to be transferred, leading to decreased performance.

There are several techniques that can be used to maintain performance balance between processor and memory:

➤ Cache optimization: Caching is a technique used to improve performance by storing frequently used data in a faster, smaller memory called a cache. By optimizing the cache, designers can

- ensure that the processor has access to the data it needs quickly, without overloading the memory.

- ➤ Memory bandwidth optimization: Memory bandwidth refers to the amount of data that can be transferred from memory to the processor in a given amount of time. By optimizing memory bandwidth, designers can ensure that the processor can access the data it needs quickly and efficiently.

- ▶ Processor speed throttling: If the processor is too fast for the memory, it may be necessary to slow down the processor to maintain performance balance. This can be achieved through techniques such as clock throttling or dynamic voltage scaling, which reduce the processor speed when it is not needed.

- ➤ **Memory optimization:** By optimizing the memory, designers can ensure that it is able to keep up with the demands of the processor. This can involve techniques such as increasing memory capacity, improving memory access times, or using specialized memory technologies such as DDR (double data rate) or HBM (high-bandwidth memory).

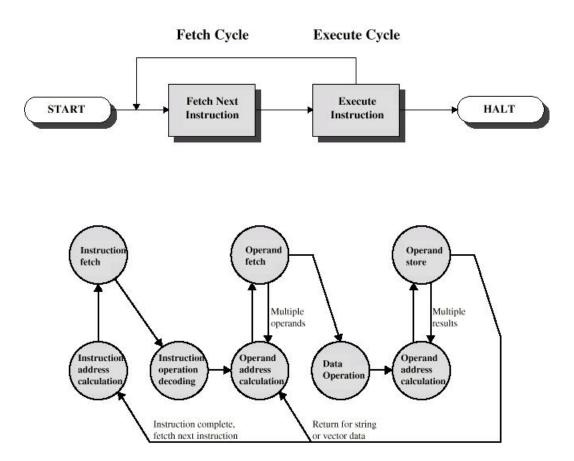

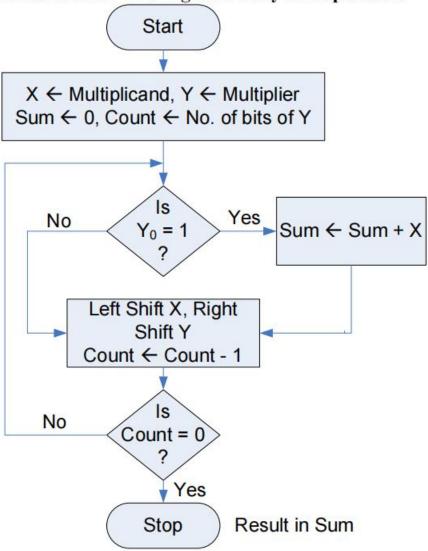

# Q. computer functions with different cycles

- Fetch: The processor retrieves the instruction from memory by sending the address of the instruction to the memory controller. The memory controller retrieves the instruction and sends it back to the processor.

- ➤ **Decode:** The processor decodes the instruction by determining what operation to perform based on the opcode and operands specified in the instruction. The operands may be registers or memory locations.

- **Execute:** The processor performs the operation specified by the instruction. This may involve arithmetic or logical operations,

data transfers between registers and memory, or branching to a different instruction.

➤ **Store:** The processor stores the result of the operation back in memory or a register. This may involve writing the result to a memory location or updating a register with the new value.

### **Computer Function (Youtube)**

The basic function performed by a computer is execution of a program, which consists of a set of instructions stored in memory.

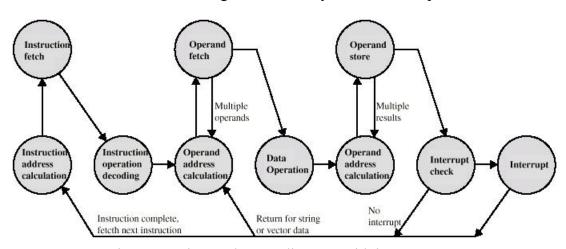

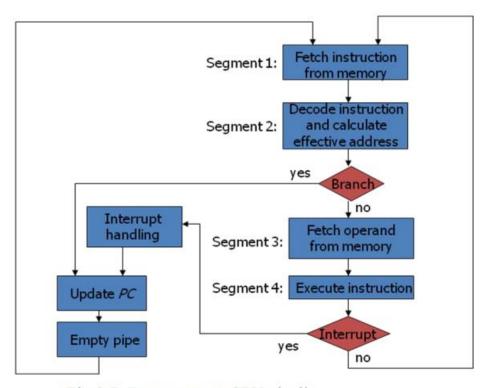

Fig: Instruction cycle state diagram

Instruction address calculation (IAC): In this state, the CPU calculates the memory address of the next instruction to be executed.

- ➤ Instruction fetch (IF): In this state, the CPU retrieves the instruction from memory address calculated in the previous step. The instruction is then stored in the instruction register (IR).

- ➤ Instruction operation decoding (IOD): In this state, the CPU decodes the instruction stored in the IR to determine what operation needs to be performed.

- ➤ Operand address calculation (OAC): In this state, the CPU calculates the memory address of any operands required by the instruction.

- ➤ Operand fetch (OF): In this state, the CPU retrieves any operands required by the instruction from memory. The operands are then stored in temporary registers or memory locations for use in the next step.

- ➤ **Data operation (DO):** In this state, the CPU performs the actual operation specified by the instruction. This may involve performing arithmetic or logical operations on the operands retrieved in the previous step.

- Operand address calculation (OAC): In this state, the CPU calculates the memory address where the result of the operation should be stored.

- ➤ Operand store (OS): In this state, the CPU stores the result of the operation back into memory or registers, depending on the nature of the instruction. This completes the execution of the instruction

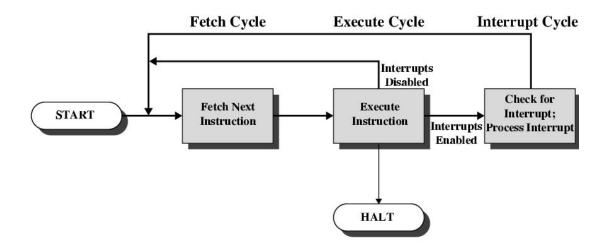

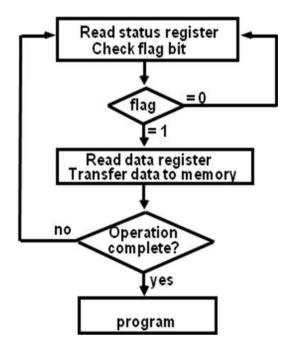

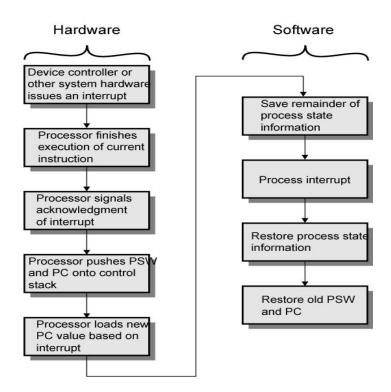

An interrupt is a signal sent to the processor by a device or program, indicating that an event has occurred that requires the processor's attention.

Fig: Instruction Cycle with Interrupts

Fig: Instruction cycle state diagram, with interrupts

- ➤ Interrupt check (IC): In this state, the CPU checks for any pending interrupts. If an interrupt is pending, the CPU saves the current state of the system and moves to the interrupt service routine (ISR).

- ➤ Interrupt: In this state, the CPU executes the code necessary to handle the interrupt. Once the ISR is complete, the CPU returns to the point in the program where the interrupt occurred..

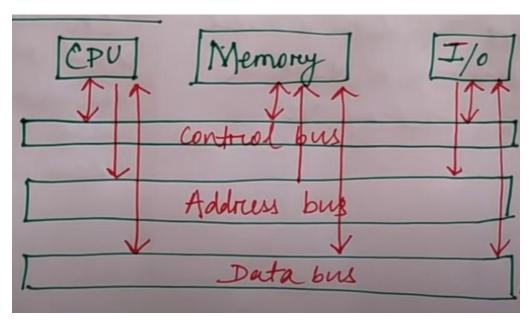

#### Interconnection structure

# Q . explain the interconnection structures of computer. Also the different operations over them?

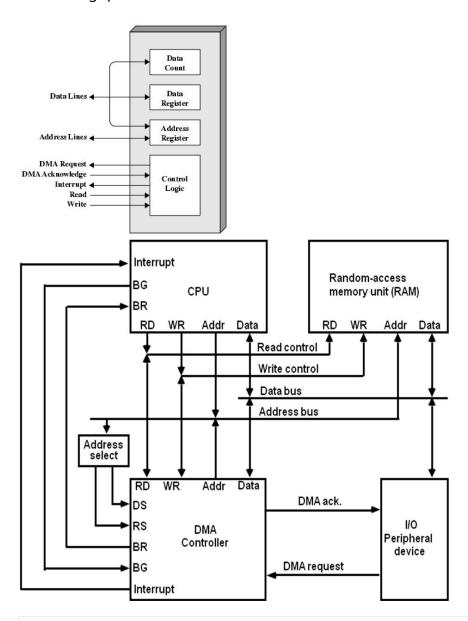

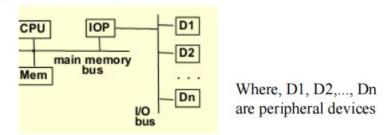

The interconnection structure of a computer system is responsible for connecting different components such as the CPU, memory, and I/O devices to facilitate the transfer of data and control signals among them.

- ➤ Memory Connection: In the case of memory, the interconnection structure receives and sends data, addresses and control signals. It also deals with timing signals to ensure that data is transferred at the right time. The memory is typically connected to the CPU and other devices through a bus system, which is a shared communication channel that enables multiple devices to communicate with each other.

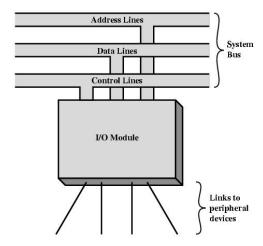

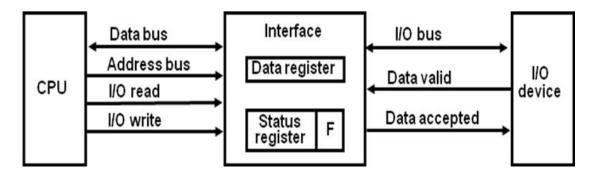

- ➤ I/o connection: Input/output devices are typically connected to the interconnection structure through I/O ports, which act as interfaces between the devices and the computer system. These ports may be specialized for specific types of devices, such as USB ports for connecting USB devices, or they may be more general-purpose, such as serial or parallel ports.

- ➤ CPU Connection: The CPU is also connected to the interconnection structure through a bus system, which allows it to communicate with other devices in the system. The bus system typically consists of multiple buses, each dedicated to a specific type of communication, such as data transfer, address transfer, or control signal transfer.

The CPU interacts with memory and I/O devices in different ways, depending on the operation being performed. Some examples of operations include:

- Instruction Fetch

- Data Read

- Data Write

- > I/O Read

- > I/O Write

#### **Bus Interconnection**

## **Q. Explain Bus interconnection?**

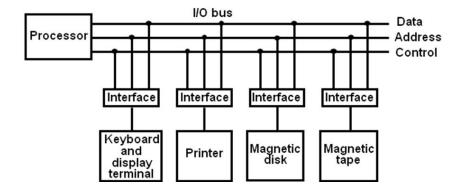

In computer organization and architecture, bus interconnection refers to the way in which different components of a computer system are connected to each other using a set of shared communication lines called a bus.

The bus is used to transfer data, instructions, and control signals between different components such as the CPU, memory, and I/O devices. The bus interconnects these components by providing a common communication pathway for the transfer of information.

There are different types of buses used in computer systems, such as the address bus, data bus, and control bus.

Address Bus: This type of bus is used to transfer memory addresses between the components of the computer system, such as the CPU and the memory. The address bus is a unidirectional bus, meaning that data can only be transferred in one direction - from the CPU to the memory. The number of

wires in the address bus determines the maximum amount of memory that can be accessed by the CPU.

- ➤ Data Bus: This type of bus is used to transfer data between the components of the computer system, such as the CPU and the memory. The data bus is a bidirectional bus, meaning that data can be transferred in both directions from the CPU to the memory and from the memory to the CPU. The number of wires in the data bus determines the maximum amount of data that can be transferred between the CPU and the memory.

- ➤ Control Bus: This type of bus is used to transfer control signals between the components of the computer system, such as the CPU and the memory. The control bus is a bidirectional bus, meaning that control signals can be transferred in both directions from the CPU to the memory and from the memory to the CPU. Control signals can include signals to indicate whether the data being transferred is a read or a write operation, signals to indicate the timing of the data transfer, and signals to indicate errors in the data transfer.

Q . limitations of single bus system to connected different devices. what does the width of data and address bus represent in a system? why is bus hierarchy required?

Here are the limitations of a single bus system:

- Single bus systems have limited bandwidth, and as more devices are connected, the available bandwidth per device decreases. This leads to slower data transfer rates and reduced system performance.

- ➤ When two or more devices try to access the bus simultaneously, leading to delays and increased system complexity.

- Single bus systems have limited scalability, and as the number of devices connected to the bus increases, the system becomes more complex and difficult to manage.

- As the number of devices connected to the bus increases. This can result in data corruption, errors, and system instability.

- Security risks are higher in single bus systems, as all devices have access to the same bus, making it more difficult to implement security measures to protect the system from external threats.

The width of the data bus determines the amount of data that can be transferred between the components of the system in a single cycle. For example, a 32-bit data bus can transfer 32 bits (or 4 bytes) of data at a time. The wider the data bus, the faster the data can be transferred between components.

The width of the address bus determines the maximum amount of memory that can be addressed by the system. For example, a 32-bit address bus can address up to 4GB of memory. The wider the address bus, the larger the amount of memory that can be addressed by the system.

Bus hierarchy is required in computer systems to improve system performance and scalability. In a complex computer system with multiple components, a single bus can become a bottleneck, leading to slow data transfer rates and reduced system performance. Bus hierarchy helps to address this issue by dividing the system into multiple buses at different levels.

### Q. Explain different elements of bus design.

The design of a bus system in a computer architecture involves several elements that must be considered to ensure efficient and reliable communication between different components. Here are some of the key elements of bus design:

- ➤ **Bus Topology:** The bus topology refers to the physical arrangement of the bus, including the wiring, connectors, and other components. The choice of topology depends on factors such as the number of devices to be connected, the distance between devices, and the bandwidth required.

- ▶ Bus Protocol: The bus protocol refers to the rules and procedures that govern how devices communicate over the bus. The protocol specifies the format of data transfer, the timing of signals, error handling, and other aspects of communication. Common bus protocols include PCI, USB, and Ethernet.

- ➤ **Bus Width:** The bus width refers to the number of data lines on the bus, which determines how much data can be transferred at a time. A wider bus allows for faster data transfer, but also requires more power and more complex hardware.

- ➤ **Bus Speed:** The bus speed refers to the frequency at which data is transferred over the bus, measured in megahertz (MHz) or gigahertz (GHz). A higher bus speed allows for faster data transfer, but also requires more power and can cause signal integrity issues.

- ➤ **Bus Arbitration:** Bus arbitration refers to the process of resolving conflicts when multiple devices try to access the bus simultaneously.

## Q. Explain different types of bus arbitration and compare them

Bus arbitration refers to the process of resolving conflicts when multiple devices try to access the bus simultaneously

- ➤ Centralized Arbitration: Centralized arbitration involves a central arbiter that controls access to the bus. In this type of arbitration, all devices must request permission from the arbiter before accessing the bus. The arbiter decides which device has priority and grants access to the bus accordingly. The advantage of centralized arbitration is that it is simple and easy to implement. However, it can also be a bottleneck, as all requests must go through a single point of control.

- ▶ Distributed Arbitration: Distributed arbitration allows each device to make its own decision about when to access the bus. In this type of arbitration, each device listens for the bus to become available and then attempts to access it. If multiple devices attempt to access the bus simultaneously, a collision occurs, and the devices must wait for a random amount of time before trying again. The advantage of distributed arbitration is that it can be more efficient than centralized arbitration, as devices can access the bus more quickly. However, it can also be more complex to implement and may require additional hardware.

- Priority Arbitration: Priority arbitration assigns a priority level to each device on the bus. The device with the highest priority is granted access to the bus first, followed by the device with the next-highest priority, and so on. If two devices have the same priority level, a collision occurs, and the devices must wait for a random amount of time before trying again. The advantage of priority arbitration is that it can be very efficient, as high-priority devices are granted access to the bus quickly. However, it can also be complex to implement and may require additional hardware.

➤ Round-Robin Arbitration: Round-robin arbitration allocates bus access to each device in turn. Each device is granted access to the bus for a fixed amount of time, after which the next device in line is granted access. The advantage of round-robin arbitration is that it is fair, as each device is given equal access to the bus. However, it can also be inefficient, as some devices may not require access to the bus as frequently as others.

#### Q. What is PCI?

PCI (Peripheral Component Interconnect) is a type of computer bus used for connecting peripheral devices to a computer's motherboard. The PCI bus is a standard interface that provides high-speed data transfer between devices, allowing them to communicate with each other and with the CPU.

# **CHAPTER 2 (18 Marks)**

# **Central Processing Unit**

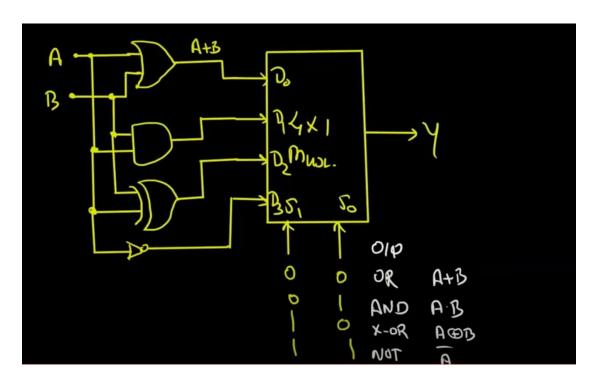

# Q. Design a 2-Bit ALU that can perform, AND, OR, X-OR and NOT operations.

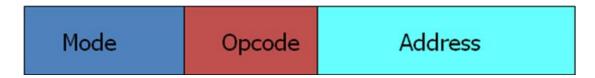

# **Instruction formats (Youtube)**

Instruction formats are a way of representing the various parts of a machine instruction in a computer's memory. They define the structure of an instruction and specify how the various fields of the instruction are encoded.

➤ An Operation code field specifies the operation to be performed such as add, subtract etc.

- ➤ An Address field specifies a memory address or a processor register, where operand is stored.

- ➤ A Mode field that specifies the way the operand or the effective address of the operand is determined.

Computers may have instructions of several different lengths containing varying number of addresses. Following are the types of instructions.

#### 1. Three address Instruction

Instruction with three operands reference is called three address instruction. Computers with three address instruction format can use each address field to specify either a processor register or a memory operand. It is also called general register organization.

| Opcode | Destination Address | Source Address 1   | Source Address 2 |

|--------|---------------------|--------------------|------------------|

|        | Three-address       | instruction format |                  |

To evaluate X = (A + B) \* (C + D)

ADD R1, A, B R1

$$\leftarrow$$

M[A] + M[B]

ADD R2, C, D R2  $\leftarrow$  M[C] + M[D]

MUL X, R1, R2 M[X]  $\leftarrow$  R1 \* R2

It is assumed that processor has two registers, R1 and R2. The symbol M[A] denotes the operand at memory address symbolized by A.

- ➤ **ADVANTAGE:** It results in short programs when evaluating arithmetic expressions.

- ➤ **DISADVANTAGE:** The instructions requires too many bits to specify 3 addresses.

#### 2. Two address Instruction

Opcode Destination Address Source Address

Two-address instruction format

Instruction with two operands reference is called two address instruction. They are the most common in commercial computers. Each address field may specify either a processor register or a memory operand.

To evaluate X = (A + B) \* (C + D)

#### 3. One address Instruction

Instruction with one operand reference is called one address instruction and use an implied accumulator (AC) register for all data manipulation. All operations is done between accumulator register and memory operand. It is called single accumulator organization.

To evaluate X = (A + B) \* (C + D)

| LOAD  | A | $AC \leftarrow M[A]$      |

|-------|---|---------------------------|

| ADD   | В | $AC \leftarrow AC + M[B]$ |

| STORE | T | $M[T] \leftarrow AC$      |

| LOAD  | C | $AC \leftarrow M[C]$      |

| ADD   | D | $AC \leftarrow AC + M[D]$ |

| MUL   | T | $AC \leftarrow AC * M[T]$ |

| STORE | X | $M[X] \leftarrow AC$      |

#### 4. Zero address Instruction

Instruction without address field/operand is known as zero address instruction. Also called stack based organization.

To evaluate X = (A + B) \* (C + D). convert first to Post fix = AB+CD+\* (link for conversion)

| PUSH | A | TOS ← A                            |

|------|---|------------------------------------|

| PUSH | В | TOS←B                              |

| ADD  |   | $TOS \leftarrow (A + B)$           |

| PUSH | C | TOS←C                              |

| PUSH | D | TOS←D                              |

| ADD  |   | $TOS \leftarrow (C + D)$           |

| MUL  |   | $TOS \leftarrow (C + D) * (A + B)$ |

| POP  | X | $M[X] \leftarrow TOS$              |

|      |   |                                    |

**Question 2**

**Question 3**

**Question 4**

Question 5

## Addressing Modes (Youtube)

Addressing modes refer to the different techniques used by computers to interpret or modify the address field of an instruction before accessing the operand.

These techniques are used to provide programming flexibility to users, reduce the number of bits needed for addressing, and enable the use of pointers, counters, indexing, and other functions. There are various modes of addressing, including those that do not require an address field at all.

In computer architecture, the **effective address** is the final memory address used to access data in memory. It is calculated by combining the base address with an offset, displacement, or index value based on the addressing mode used. The effective address is determined by the addressing mode of the instruction, and it is the actual address of the operand used by the CPU to retrieve or store data during program execution. It is an important concept as it determines the location of data in memory.

# 1. Implied addressing mode

- ➤ Implied addressing mode is a simple addressing mode used in computer programming where the instruction does not explicitly specify the operand's memory address.

- ➤ The operand's address is instead implied by the instruction opcode itself or the context in which the instruction is executed.

Eg:

- > CLC clears the carry flag in the processor's status register

- > INX increments the value of the X register by one

| Instruction |  |

|-------------|--|

| Opcode      |  |

- > Advantage: no memory reference.

- > Disadvantage: limited operand

## 2. Immediate addressing mode

- ➤ The operand value is directly included in the instruction itself, typically as a constant.

- ➤ The immediate addressing mode is used for operations that require constant values, such as adding a fixed value to a register or setting a flag.

- Immediate addressing mode is often used for arithmetic and logical operations

- No computation required to calculate EA

E.g. ADD 5

- Add 5 to contents of accumulator

- 5 is operand

Instruction

Opcode Operand

Eg : MVI B, 50H ( B <- 50H)

- > Advantage: no memory reference.

- > Disadvantage: limited operand

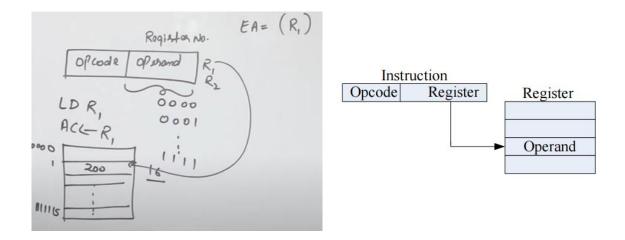

# 3. Register direct addressing mode

- In direct register addressing mode, the operand is stored directly in the register specified in the instruction.

- > Register No is written in Instruction.

## For example

- ➤ MOV R1, #10 moves the constant value 10 into register R1

- ➤ ADD R1, R2 adds the contents of register R2 to the contents of register R1 and stores the result in R1

- ➤ SUB R1, #5 subtracts the constant value 5 from the contents of register R1 and stores the result in R1

**Advantage:** no memory reference. **Disadvantage:** limited address space

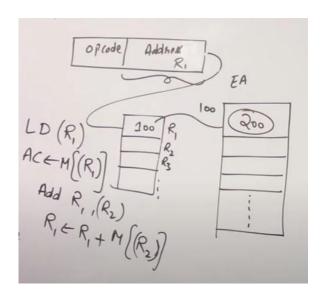

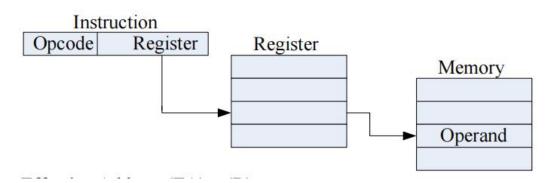

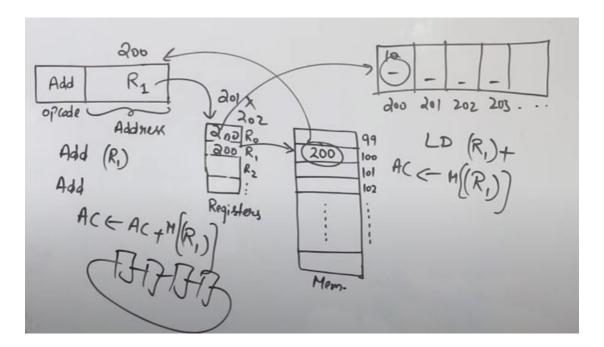

# 4. Register Indirect addressing mode

- ➤ In indirect register addressing mode, the memory address of the operand is stored in the register specified in the instruction.

- ➤ Register indirect addressing mode is useful for accessing data in memory without knowing the actual memory address of the operand.

$$EA = (R1)$$

- ➤ LDR R1, [R2] loads the contents of the memory address stored in register R2 into register R1

- > STR R1, [R2] stores the contents of register R1 at the memory address stored in register R2

- ➤ ADD R1, [R2] adds the contents of the memory address stored in register R2 to the contents of register R1 and stores the result in R1

Advantage: Large address space.

**Disadvantage:** Extra memory reference

### 5. Auto increment or decrement addressing mode

- > This is similar to register indirect mode except that the register is incremented or decremented after (or before) its value is used to access memory.

- ➤ When the address stored in the registers refers to a table of data in memory, it is necessary to increment or decrement the registers after every access to the table.

- ➤ This can be achieved by using the increment or decrement instruction. In some computers it is automatically accessed.

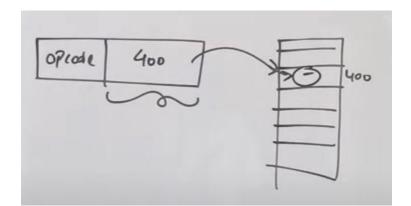

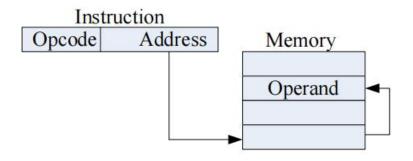

# 6. Direct Addressing Mode

- Actual address is given in the instruction

- Use to access variables

Effective Address (EA) = A

## For example:

LDA 4000H - loads the contents of memory location 4000H into the accumulator.

ADD 4001H - adds the contents of memory location 4001H to the accumulator

Advantage: Simple.

Disadvantage: limited address field

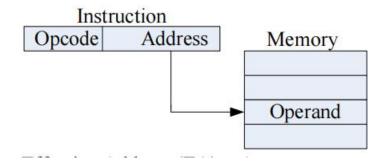

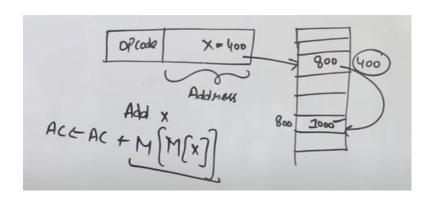

# 7. Indirect Addressing Mode

- ➤ The address of the memory location to be accessed is not specified directly, but rather indirectly through a register or memory location that holds the address.

- > Used to implement pointers and passing parameters.

EA = (X)

Eg:

MOV AX, [BX] - This instruction moves the contents of the memory location whose address is stored in the BX register into the AX register. Here, BX acts as a pointer to the memory location that contains the data.

**Advantage:** Flexibility. **Disadvantage:** Complexity

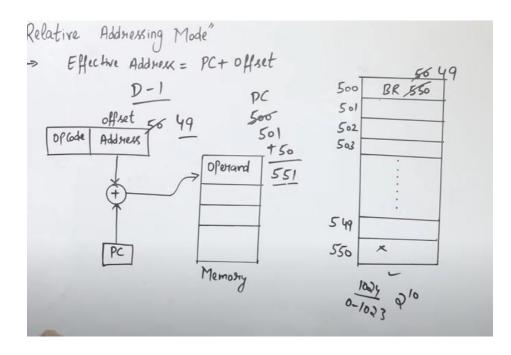

# 8. Relative Addressing Mode

> Used for program control instructions like branch and jump

We give offset in address and when we give 50 in it the PC is 500 and the data should be fetched from 550 because and program should branch to BR 550 but PC will increase to 501(since PC always gives address of next instruction) and if we give 50 off set then after 50 displacement PC - 551 which is not 550 which we need so offset is give 1 less that is 49 to reach 550 and fetch data.

The major **advantage** of relative addressing mode is that it allows programs to access memory locations without having to know their absolute addresses, making the programs more portable and easier to write.

The major **disadvantage** of relative addressing mode is that it is limited to accessing memory locations that are located at a fixed distance from the current instruction, so it cannot be used to access memory locations that are farther away.

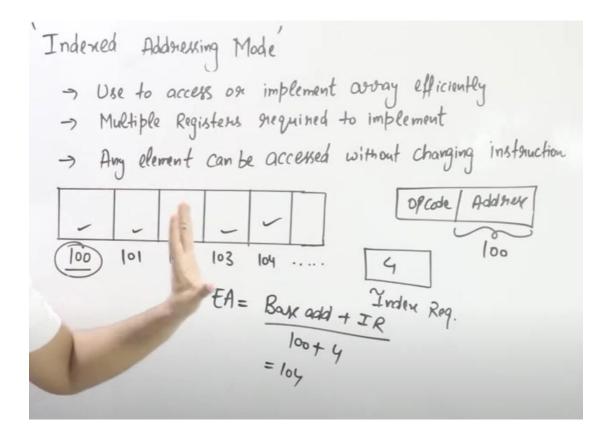

## 9. Indexed Addressing Mode

- ➤ Here fix the base address of the array say 100

- ➤ Here EA=BA+IR

- If we want to access  $4^{th}$  element of array then set Index register to 4 the EA = 100+4 = 104 for  $6^{th}$  element set IR= 6 and so on.

The major **advantage** of indexed addressing mode is that it allows for more flexible memory access than direct or immediate addressing modes, as it can be used to access memory locations that are located at a variable distance from the base address stored in the register.

The major **disadvantage** of indexed addressing mode is that it can be slower than direct addressing mode due to the additional time required to compute the address by adding the offset or index value to the base address stored in the register.

# Q. Explain different types of data manipulation instructions with example.

Data manipulation instructions are used in computer architecture and programming to perform various operations on data stored in memory or registers. Here are some different types of data manipulation instructions along with examples:

- **1.Arithmetic Instructions:** Arithmetic instructions are used to perform arithmetic operations on data. Examples include:

- ➤ ADD AX, BX; Add the contents of the BX register to the AX register

- SUB CX, DX; Subtract the contents of the DX register from the CX register

- MUL BX; Multiply the contents of the AX register by the BX register

- **2.Logical Instructions:** Logical instructions are used to perform logical operations on data, such as AND, OR, and NOT. Examples include:

- ➤ AND AX, BX; Perform a bitwise AND operation on the contents of the AX and BX registers

- OR CX, DX; Perform a bitwise OR operation on the contents of the CX and DX registers

- NOT BX; Perform a bitwise NOT operation on the contents of the BX register

- **3.Shift and Rotate Instructions:** Shift and rotate instructions are used to shift or rotate the bits of data to the left or right. Examples include:

- > SHL AX, 2; Shift the bits in the AX register two positions to the left

- > SHR BX, 3; Shift the bits in the BX register three positions to the right

- ➤ RCL CX, 1; Rotate the bits in the CX register one position to the left through the carry flag

- **4.Data Transfer Instructions:** Data transfer instructions are used to transfer data between memory and registers, or between registers. Examples include:

- MOV AX, BX; Move the contents of the BX register to the AX register

- ➤ MOV [SI], AX; Move the contents of the AX register to the memory location specified by the SI register

- XCHG BX, CX; Exchange the contents of the BX and CX registers

## Q. Explain the component of CPU.

The CPU, or Central Processing Unit, is the "brain" of a computer system, responsible for executing instructions and performing calculations. It consists of several components, including:

- ➤ Control Unit (CU): The control unit is responsible for managing the operation of the CPU, fetching instructions from memory, decoding them, and executing them. It controls the flow of data within the CPU and between the CPU and other components of the computer system.

- ➤ **Arithmetic Logic Unit (ALU):** The ALU is responsible for performing arithmetic and logical operations on data. It can perform operations such as addition, subtraction, multiplication, division, and comparison.

- ➤ **Registers:** Registers are small, high-speed storage locations located within the CPU that hold data and instructions being processed by the CPU. There are several types of registers, including:

- **Program Counter (PC):** The program counter holds the address of the next instruction to be executed.

- Instruction Register (IR): The instruction register holds the current instruction being executed.

- Accumulator (ACC): The accumulator holds data being processed by the ALU.

- **General-Purpose Registers:** General-purpose registers can be used to hold data or addresses.

- ➤ Cache: Cache is a small, high-speed memory located within the CPU or on the CPU chip that stores frequently accessed data and instructions. It is used to improve the performance of the CPU by reducing the time it takes to access data from memory.

- ➤ **Bus Interface Unit (BIU):** The bus interface unit is responsible for communicating with other components of the computer system through the system bus. It fetches data and instructions from memory and writes data to memory.

## Q. Write down the need for addressing modes.

- Addressing modes allow for efficient and flexible memory access by specifying how to access data and instructions stored in memory.

- Addressing modes are used to support program control flow, such as branching and jumping to different locations in memory.

- Addressing modes provide flexibility and versatility in performing data manipulation operations.

- ➤ Addressing modes help to optimize code by allowing for efficient memory access and minimizing the number of instructions required to perform operations.

- Addressing modes can be designed to work within the limitations of the hardware, such as the number of registers, memory size, or processor speed.

| RISC Architecture                                                   | CISC Architecture                                                                                                                                                 |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RISC stands for Reduced Instruction Set Computing.                  | CISC stands for Complex Instruction Set Computing.                                                                                                                |

| ·                                                                   | CISC processors have a large and complex set of instructions.                                                                                                     |

| · ·                                                                 | CISC architecture emphasizes complex instructions that can perform multiple operations in one instruction.                                                        |

| . , , ,                                                             | CISC processors typically have a smaller number of registers, and some operations are performed directly on memory.                                               |

| RISC processors rely heavily on compilers to optimize code.         | CISC processors rely on hardware to optimize code.                                                                                                                |

| for applications that require high performance and efficient use of | CISC architecture is more suited for applications that require complex operations and large amounts of memory, such as database systems and scientific computing. |

| Heavily Pipelined                                                   | Not/less Pipelined                                                                                                                                                |

# **CHAPTER 3 (10 MARKS)**

## **CONTROL UNIT**

| <b>Control Memory</b>                                                                          | Main Memory                                                                                      |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Also known as "control store" or<br>"microcode memory"                                         | Also known as "RAM" or "primary memory"                                                          |

| Stores microcode, which provides the control signals for the processor to execute instructions | Stores data and instructions that are currently being used by the processor                      |

| Non-volatile, meaning that its contents are retained even when power is turned off             | Volatile, meaning that its contents are lost when power is turned off                            |

| Small in size compared to main memory                                                          | Much larger in size compared to control memory                                                   |

| Access time is very fast                                                                       | Access time is relatively slower compared to control memory                                      |

| Typically used in embedded systems, where the microcode is fixed and doesn't change            | Used in all types of computers, where both data and instructions need to be stored and retrieved |

Control memory, also known as control store or microcode memory, is a type of computer memory that stores microcode/microprogram. Microcode is a low-level code that provides the control signals for the processor to execute instructions.

| Hardwired Control Unit                                                                    | Micro-Programmed Control Unit                                                                          |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Uses fixed logic gates and combinational circuits to generate control signals             | Uses microcode to generate control signals                                                             |

| Designed using a hardware description language (HDL) and implemented directly in hardware | Implemented using a control store, which contains microcode                                            |

| Faster execution since it does not require memory access to generate control signals      | Slower execution compared to hardwired control unit since it requires memory access to fetch microcode |

| Difficult to modify or update since changes require physical changes to the hardware      | Easily modifiable since changes can<br>be made to the microcode without<br>changing the hardware       |

| Used in simple processors with a limited instruction set                                  | Used in more complex processors with a larger instruction set                                          |

| Lower cost since it requires less<br>memory and has simpler<br>implementation             | Higher cost since it requires more memory to store microcode and has a more complex implementation     |

# **Microprogrammed control unit:**

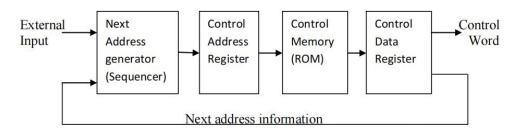

Fig 3-1: Microprogrammed Control Organization

A micro-programmed control unit is a type of control unit that uses a microprogram to control the operations of a computer. Here's how it works:

When an instruction is fetched from memory, the microprogrammed control unit uses the sequencer to generate a sequence of microinstructions that define the operations to be performed by the computer. The CAR holds the address of the next microinstruction to be executed, which is fetched from the control memory. The CDR holds the data required for the microinstruction being executed, which is used by the computer to perform the operation.

The control word is used to specify the microinstruction to be executed, including the address of the next microinstruction and any other control signals required for the operation. The microprogrammed control unit then executes the microinstruction, updating the CAR with the address of the next microinstruction to be executed, and repeating the process until the instruction is completed.

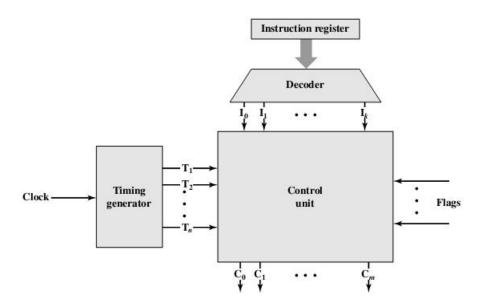

#### **Hardwired Control Unit**

A hardwired control unit is a component of a computer's central processing unit (CPU) responsible for managing the execution of instructions. It typically contains the following components:

- ➤ **Timing generator:** This component generates timing signals that synchronize the operations of the CPU's different components, such as the control unit, arithmetic logic unit (ALU), and memory unit.

- Control unit (CU): The CU is responsible for fetching instructions from memory, decoding them, and then executing them. It uses the timing signals generated by the timing generator to coordinate its operations with those of other components.

- ➤ **Decoder:** The decoder is responsible for decoding the instructions fetched by the CU. It translates the instruction into a series of control signals that are sent to other components of the CPU, such as the ALU and memory unit.

- ➤ Instruction register (IR): The IR is a small memory unit that temporarily stores the instruction being executed by the CPU. It is used by the CU to decode the instruction.

- Flags: Flags are special registers that contain the status of the CPU. They are used by the CPU to indicate whether certain conditions have been met, such as whether an arithmetic operation resulted in a zero value or whether an instruction caused an overflow.

In summary, a hardwired control unit uses a timing generator to coordinate the operations of the CPU's different components, a CU to fetch, decode, and execute instructions, a decoder to translate instructions into control signals, an IR to temporarily store instructions, and flags to indicate the status of the CPU.

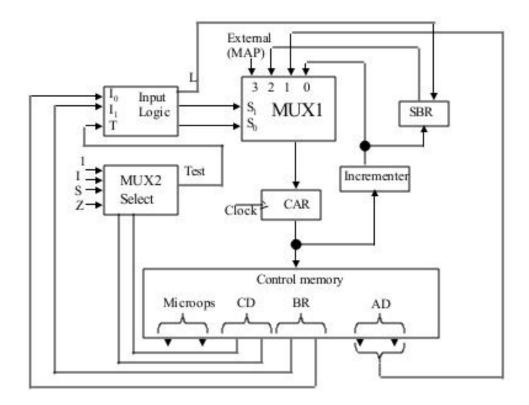

#### **Microprogram Sequencer**

- Q. Describe how address of control memory is selected.

- Q. How address of micro instruction is generated by next address generator in control unit? Explain with suitable diagram.

A microprogram sequencer is a crucial component of a microprogrammed control unit responsible for selecting the next address to be read from the control memory so that a microinstruction can be fetched and executed.

It consists of several parts, including a control memory, a subroutine register (SBR), two multiplexers, and an input logic circuit.

The control memory stores microinstructions that are executed by the control unit. The microprogram sequencer selects the address of the next microinstruction to be executed by the control unit. The subroutine register (SBR) holds the return address for subroutine calls and returns.

The two multiplexers in the microprogram sequencer select an address from four different sources. The first multiplexer selects an address from one of the four sources and routes it to the Current Address Register (CAR). The second multiplexer tests the value of the selected status bit and applies the result to an input logic circuit.

The output from the CAR provides the address for the control memory. The contents of the CAR are incremented and applied to one of the multiplexer's inputs and to the SBR. Although the block diagram in the text shows a single SBR, a typical microprogram sequencer will have a register stack about four to eight levels deep to support push, pop, and stack pointer operations for subroutine calls and returns.

The CD (Condition) field of the microinstruction selects one of the status bits in the second multiplexer. The Test variable, which can be either 1 or 0, together with the two bits from the Branch (BR) field, goes to an input logic circuit to determine the type of operation to be executed.

Overall, the microprogram sequencer operates by selecting the address of the next microinstruction to be executed by the control unit. It uses two multiplexers to select an address from four different sources and test the value of the selected status bit. The contents of the CAR are incremented and applied to one of the multiplexer's inputs and to the SBR. The CD field of the microinstruction selects one of the status bits in the second multiplexer, and the Test variable, together with the two bits from the BR field, goes to an input logic circuit to determine the type of operation to be executed.

### Q. What factors cause micro-programmed control unit to be selected over hardwired control unit

- Micro-programmed control units are more flexible than hardwired control units.

- Micro-programmed control units can be easier to design and implement.

- Micro-programmed control units are easier to test and debug than hardwired control units.

- Micro-programmed control units can be developed more quickly and at a lower cost than hardwired control units because they require less design and development effort.

#### **CHAPTER 4 (10 MARKS)**

#### **Pipeline and Vector Processing**

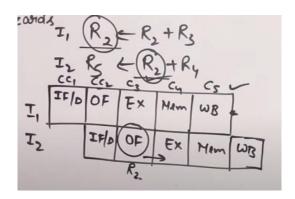

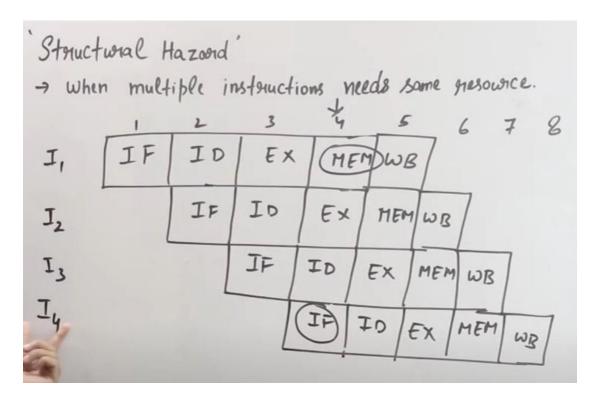

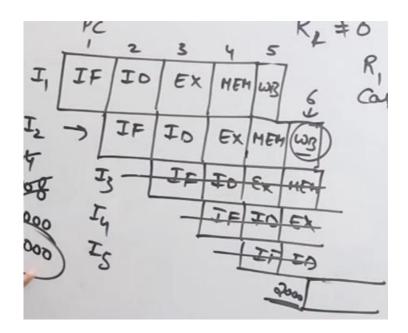

# Q. What is pipeline? How performance of computer is increased using pipelining? Explain with example.

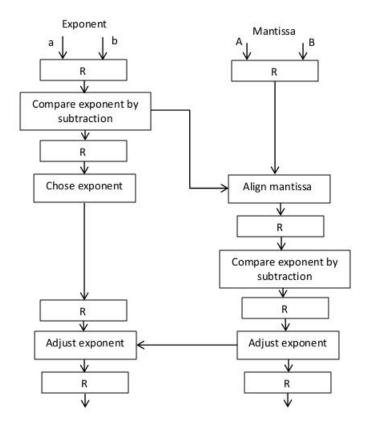

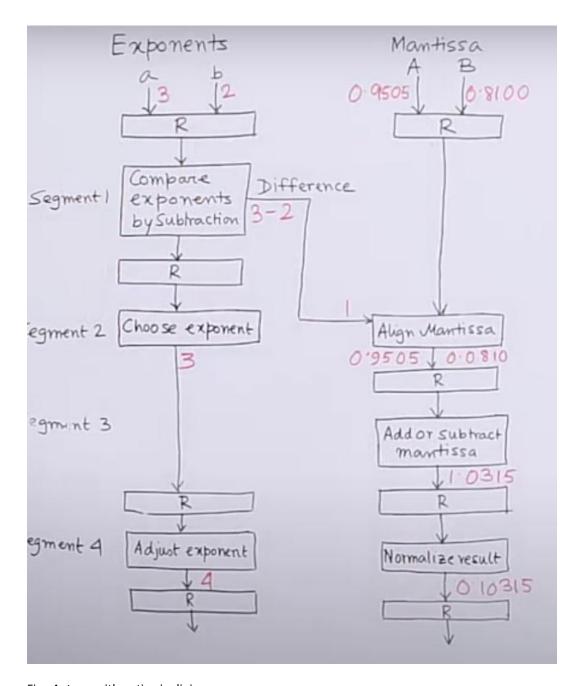

Pipelining is a technique for improving the performance of computer processors by dividing a complex task into smaller subtasks and processing them concurrently. In a pipelined system, the processing of a task is divided into a series of stages, and each stage performs a specific operation on the task.

For example, consider a simple pipeline for processing a list of numbers:

- In the first stage, the numbers are read from memory and loaded into a register.

- In the second stage, the numbers are sorted.

- In the third stage, the sorted numbers are written back to memory.

In a non-pipelined system, each of these stages would be performed one after the other, which would take a long time to complete. However, in a pipelined system, each stage can be performed concurrently on a different set of data.

For example, while the first stage is reading the numbers from memory, the second stage can be sorting the previously read numbers, and the third stage can be writing the already sorted numbers back to memory. This results in a significant improvement in the processing speed and efficiency of the system.

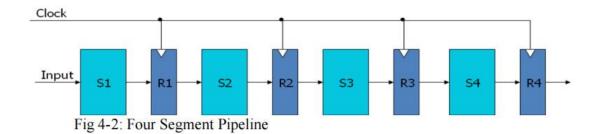

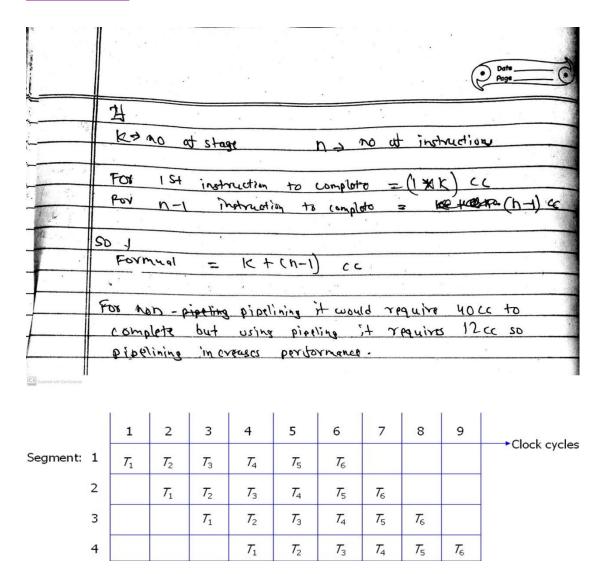

The general structure of a four-segment pipeline is illustrated in Fig. 4-2. We define a task as the total operation performed going through all the segments in the pipeline.

Here IR (Instruction Registers i.e R1,R2..) are used to store the outputs of each stage

#### For 4-Stage Pipelining:

- **Instruction Fetch:** In this stage, the processor fetches the instruction from memory.

- **Instruction Decode:** In this stage, the processor decodes the instruction and determines the operations to be performed.

- **Execute:** In this stage, the processor performs the required operations on the data, such as arithmetic or logical operations.

- Write-Back: In this stage, the results of the execute stage are written back to memory or the processor's registers.

The behavior of a pipeline can be illustrated with a space-time diagram. It shows the segment utilization as a function of time.

For a 5-stage pipelining architecture, the five stages are typically:

• **Instruction Fetch (IF):** The processor fetches the instruction from memory.

- **Instruction Decode (ID):** The processor decodes the instruction and determines the operations to be performed.

- **Execute (EX):** The processor performs the required operations on the data, such as arithmetic or logical operations.

- Memory Access (MEM): The processor accesses memory, if required by the instruction.

- Write-Back (WB): The results of the execute stage are written back to memory or the processor's registers.

(6 stage pipelining ma write back pachi commit huncha)

|         | Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| -       | Pipelining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|         | The state of the s |  |  |  |  |  |  |

|         | Par la                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| SI      | 24 12 23 24 25 26 27 28 - It Strass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 27      | 21 22 24 25 26 27 28 -20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 18th 23 | I 12 13 24 25 26 24 28 + RY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 54      | II I2 I3 24 I5 26 IA 28 + MEM 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 55      | 1 7413 41 3 40 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|         | & state pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|         | Time-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

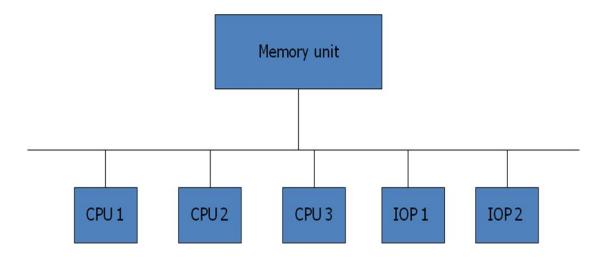

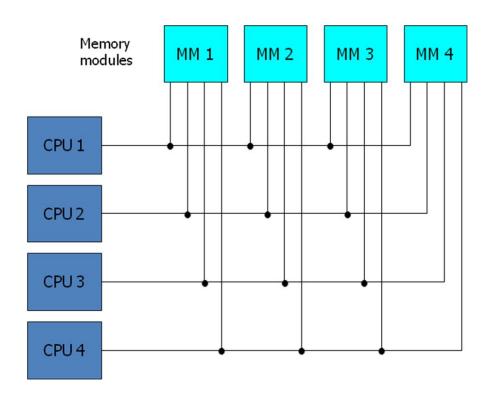

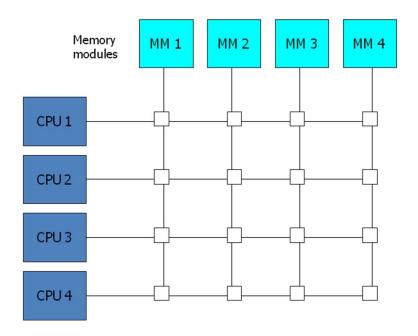

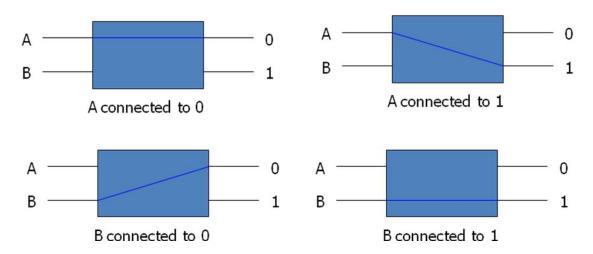

|         | Fig. space time diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |